块表的地址变换机构

时间局部性:如果执行了程序中的某条指令,那么不久后这条指令很有可能再次执行;如果某个数据被访问过,不久之后该数据很可能再次被访问。(因为程序中存在大量的循环)

空间局部性:一旦程序访问了某个存储单元,在不久之后,其附近的存储单元也很有可能被访问。(因为很多数据结构在内存中都是连续存放的)

在基本地址变换机构中,每次要访问一个逻辑地址,都需要查询内存中的页表。由于局部性原理,可能连续很多次查到的都是同一个页表项。既然如此,能否利用这个特性减少访问页表的次数呢?

什么是块表(TLB)

块表,又称联想寄存器(TLB),是一种访问速度比内存块很多的高速缓冲寄存器,用来存放当前访问的若干页表项,以加速地址变换的过程。于此对应,内存中的页表长称为慢表。

引入块表后,地址的变换过程

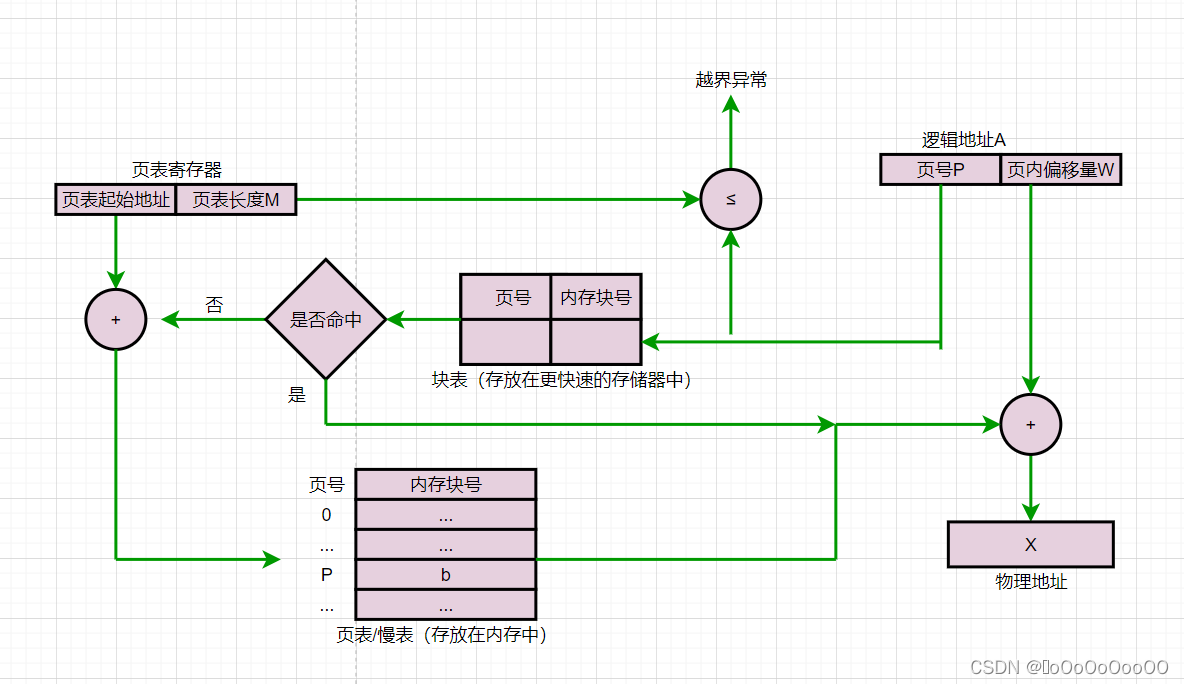

1.CPU给出逻辑地址,由某个硬件算得页号、页内偏移量,将页号与块表中的所有页号进行比较。

2.如果找到匹配的页号,说明要访问的页表项在块表中有副本,则直接从中取出该页对应的内存块号,再将内存块号与页内偏移量拼接形成物理地址,最后,访问该物理地址对应的内存单元。因此,若块表命中,则访问某个逻辑地址仅需一次坊存即可。

3.如果没有找到匹配的页号,则需要访问内存中的页表,找到对应页表项,得到页面存放的内存块号,再将内存块号与页内偏移量拼接形成物理地址,最后,访问该物理地址对应的内存单元。因此,若块表未命中。则访问某个逻辑地址需要两次访存(注意:在找到页表项后,应同时将其存入块表,以便后面可能的再次访问。但若块表已满,则必须按照一定的算法对旧的页表项进行替换)

由于查询块表的速度比查询页表的速度块很多,因此只要块表命中,就可以节省很多时间。

因为局部性原理,一般来说块表的命中率可以达到90%以上。

版权声明:本文为LOOKTOMMER原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。